Introduction

Software Defined Radios (SDRs) are radios that are easily reconfigurable through software, thus replacing many radio hardware features. For my Hardware Design and Communications course (ECE295), teams of three students were to design one of four subsystems for the portion of a SDR that interfaces with the physical radio signal. This document outlines our design process and what I've learned along the way about hardware design and development!

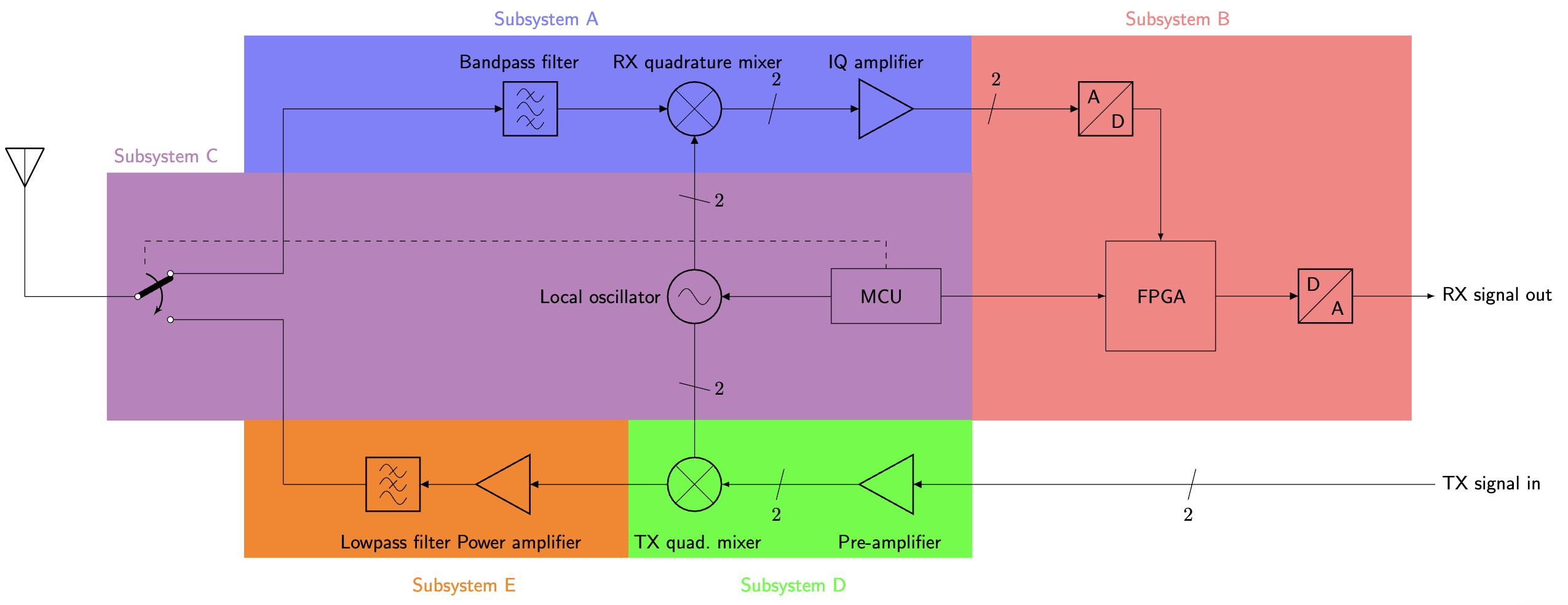

The SDR was composed of the following subsystems:

- RX Quadrature Mixer [Subsystem A]

- Demodulator [Subsystem B]

- Local Oscillator and User/Computer Interface [Subsystem C]

- TX Quadrature Mixer [Subsystem D]

- X Power Amplifier and Filter [Subsystem E]

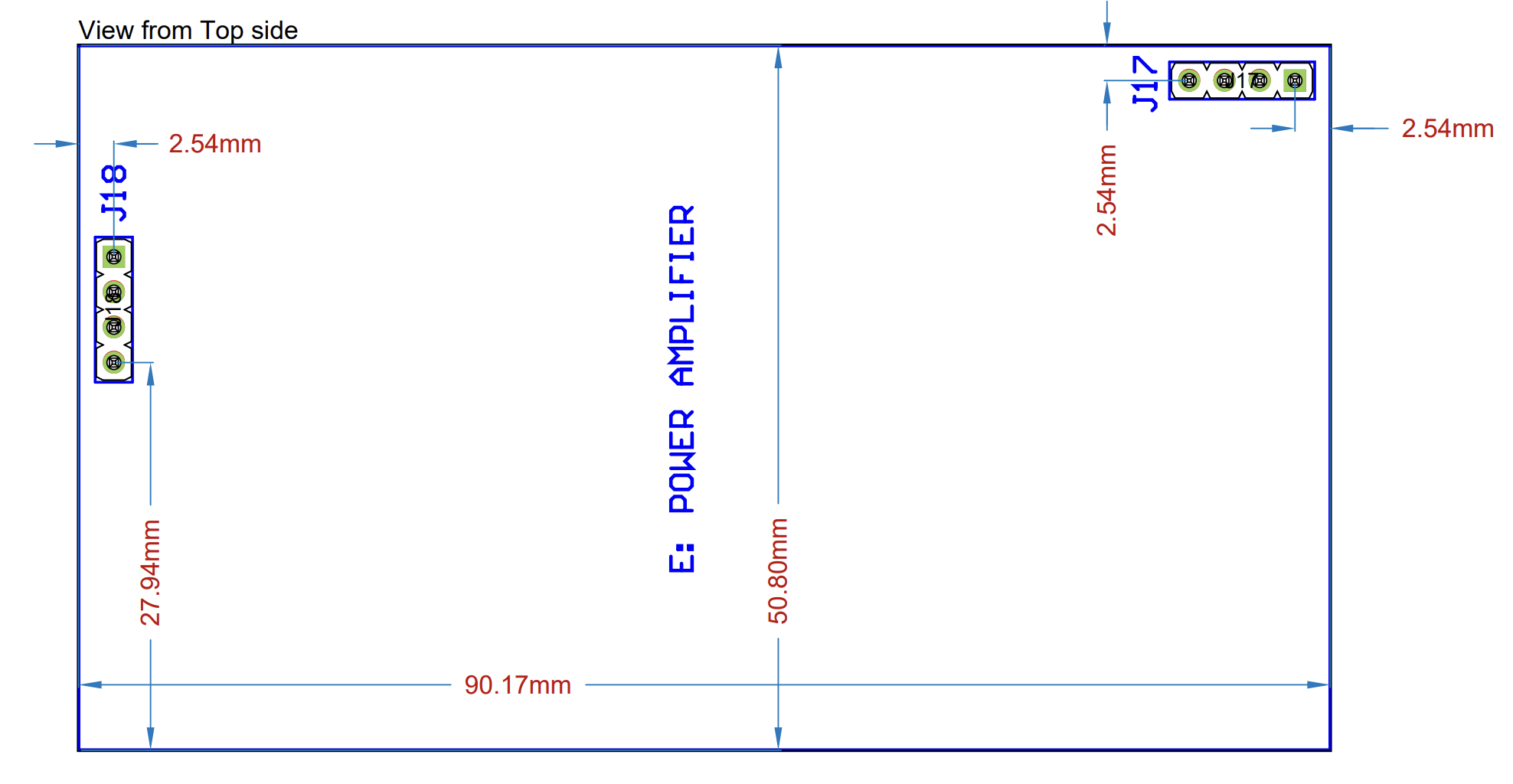

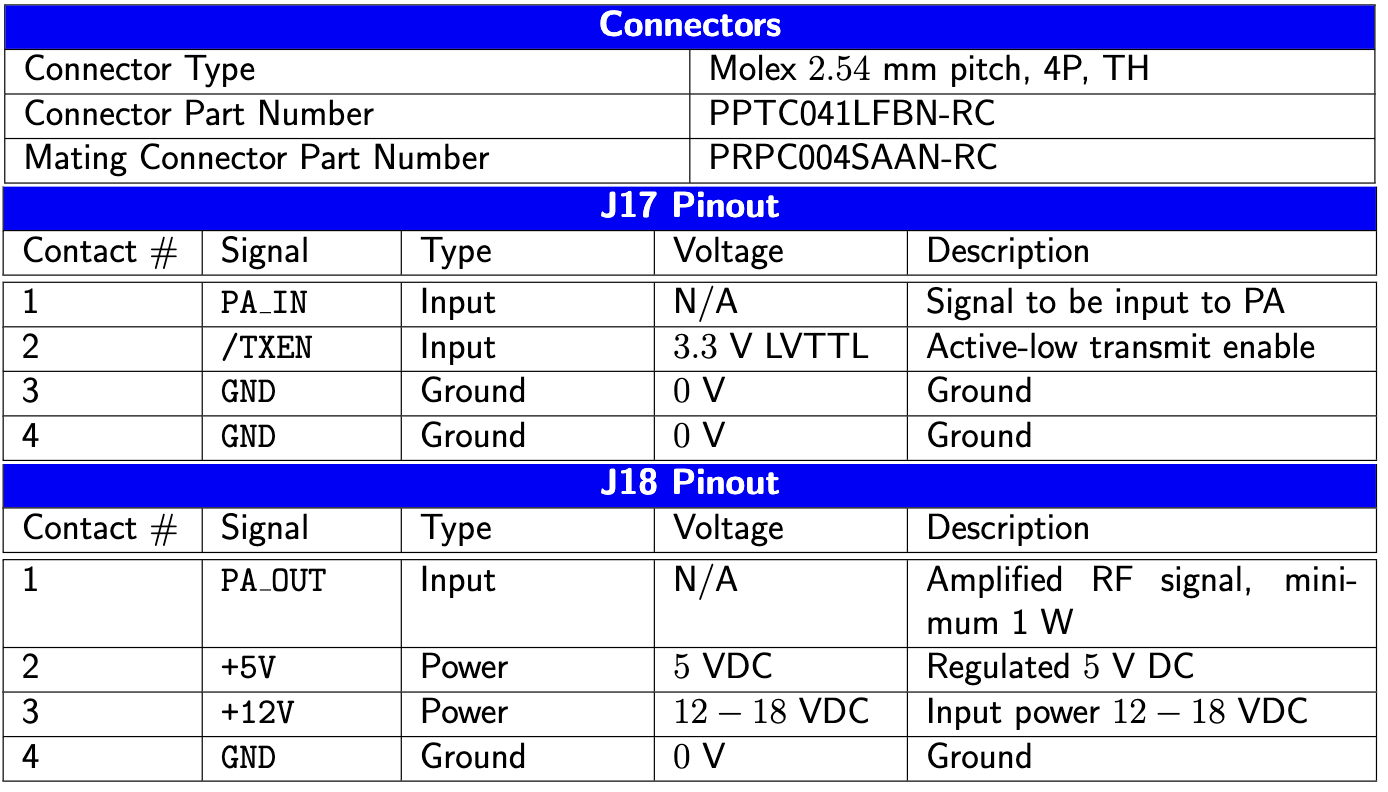

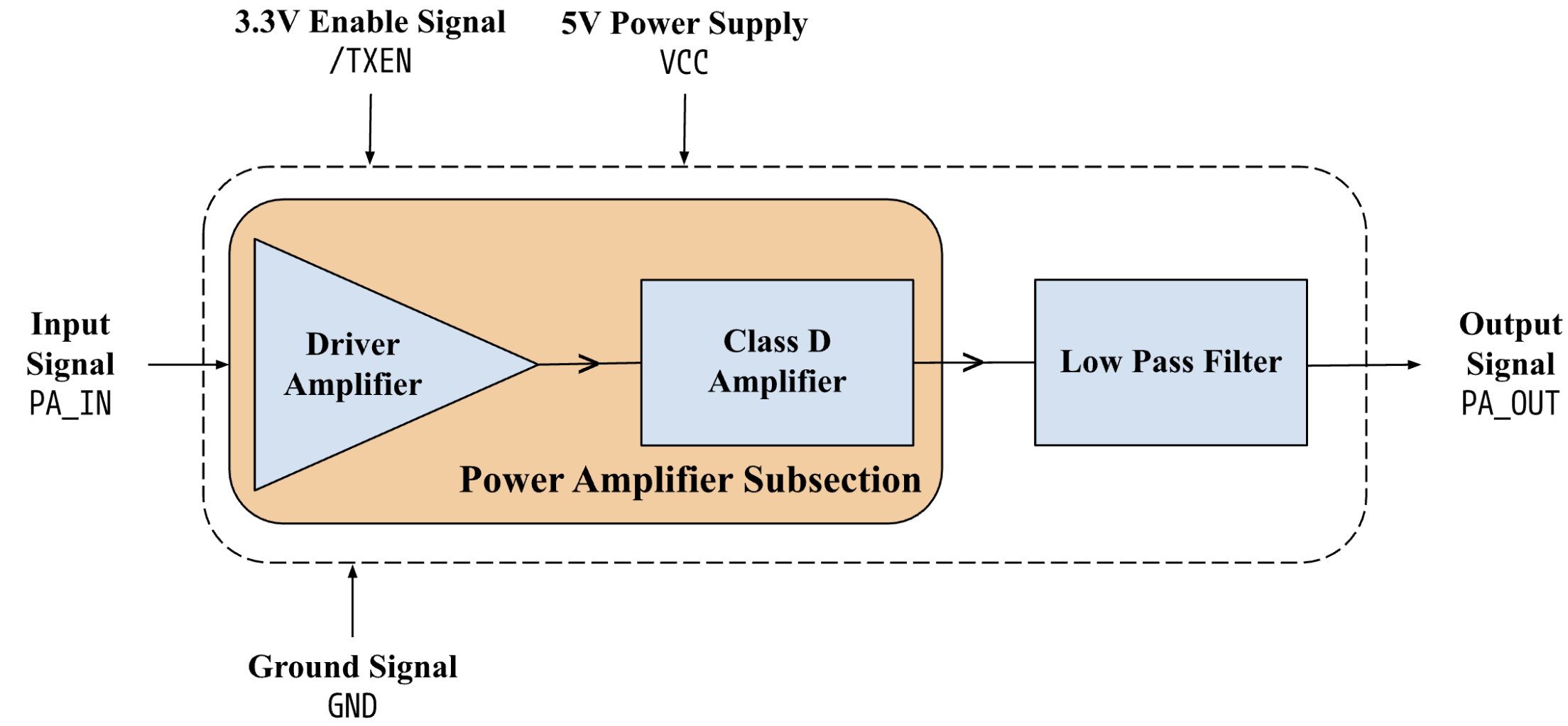

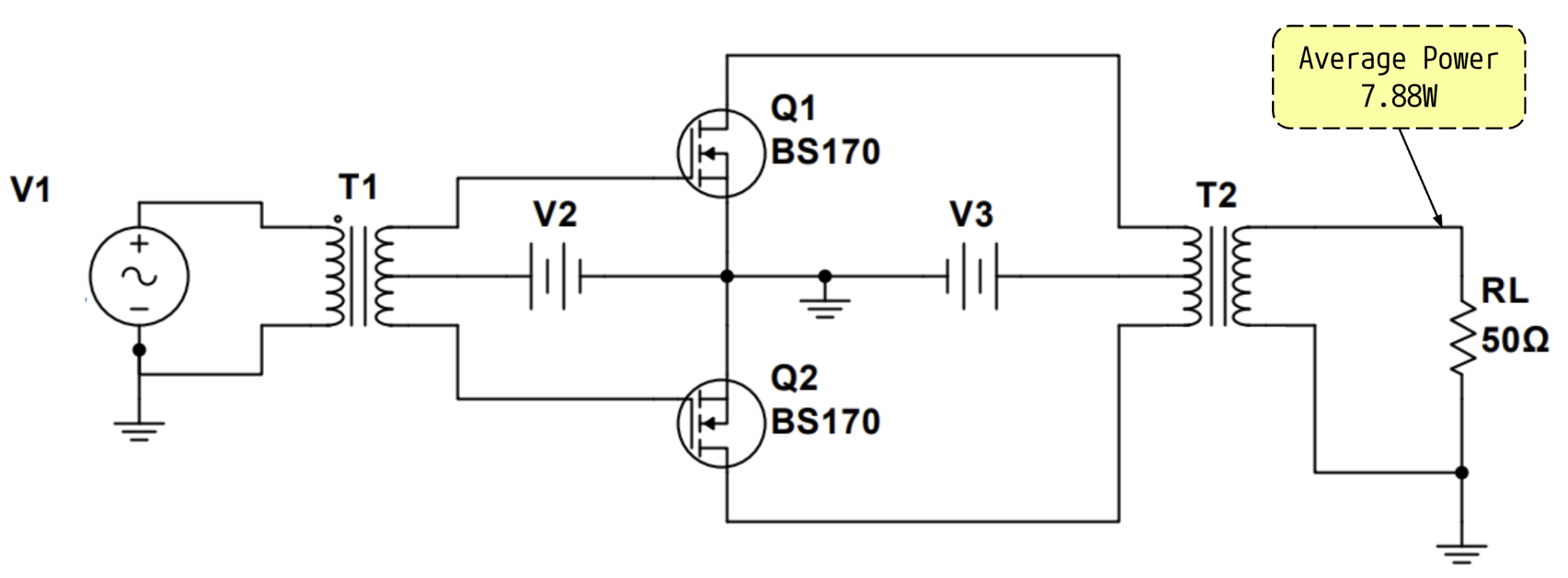

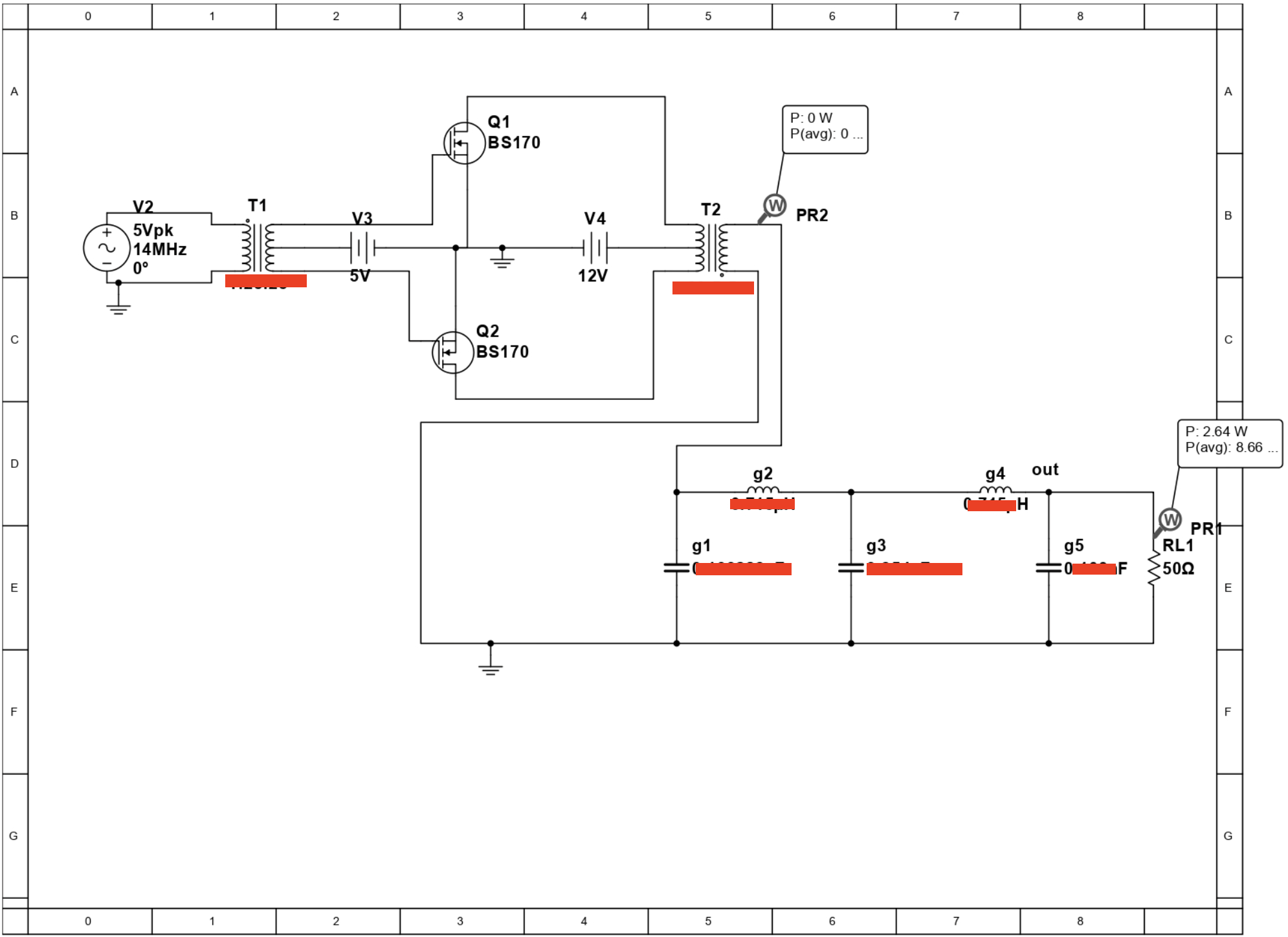

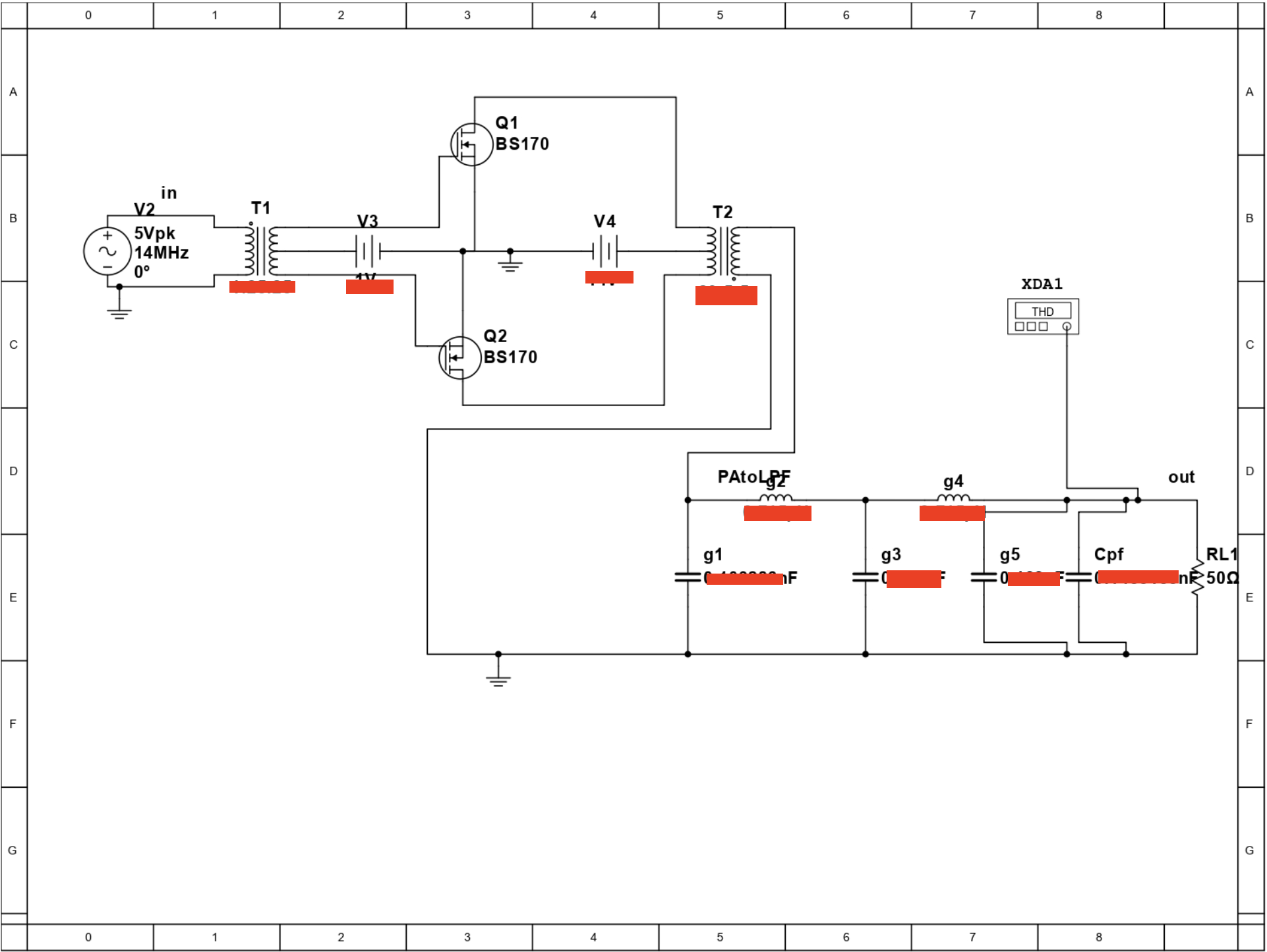

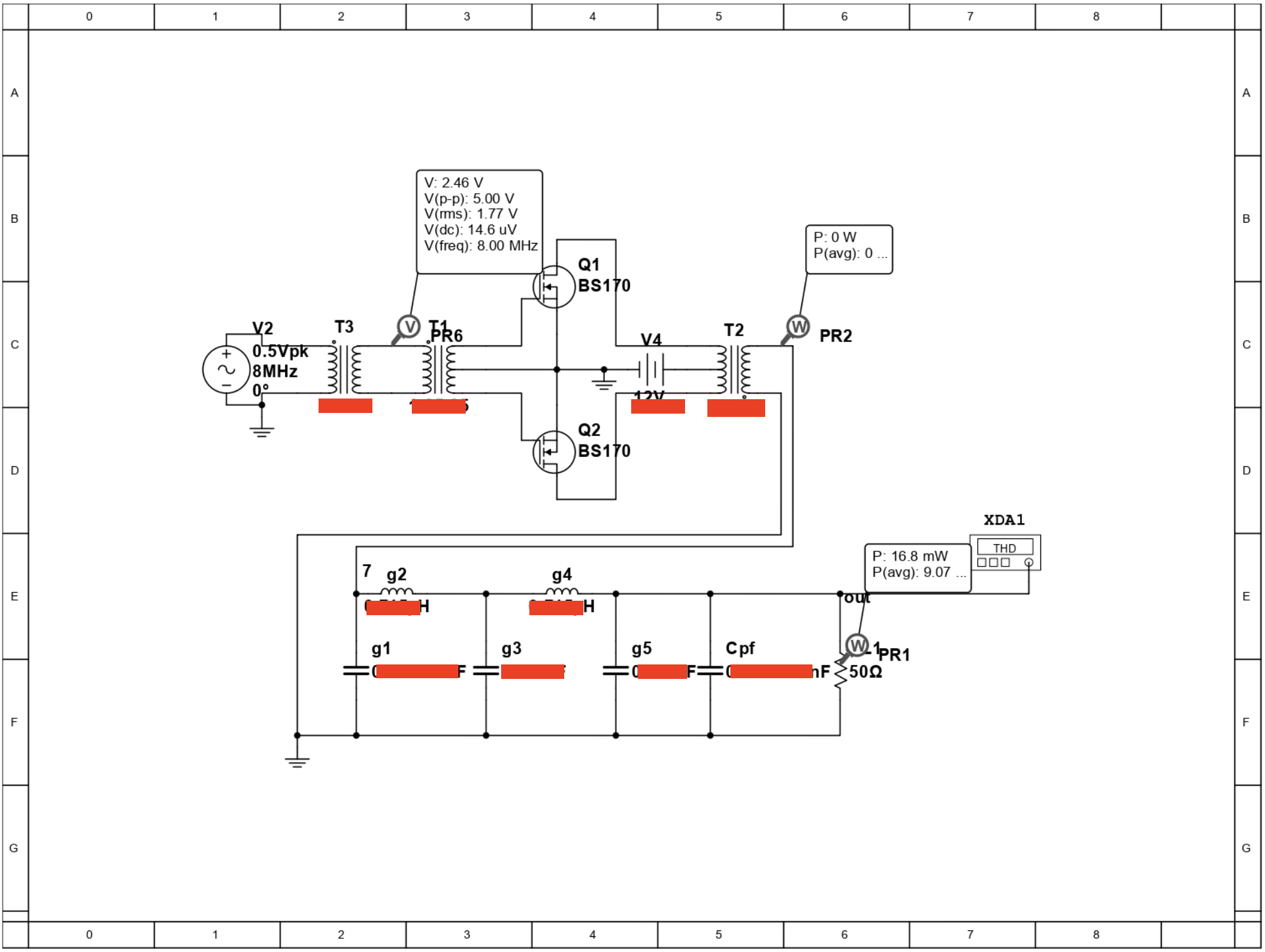

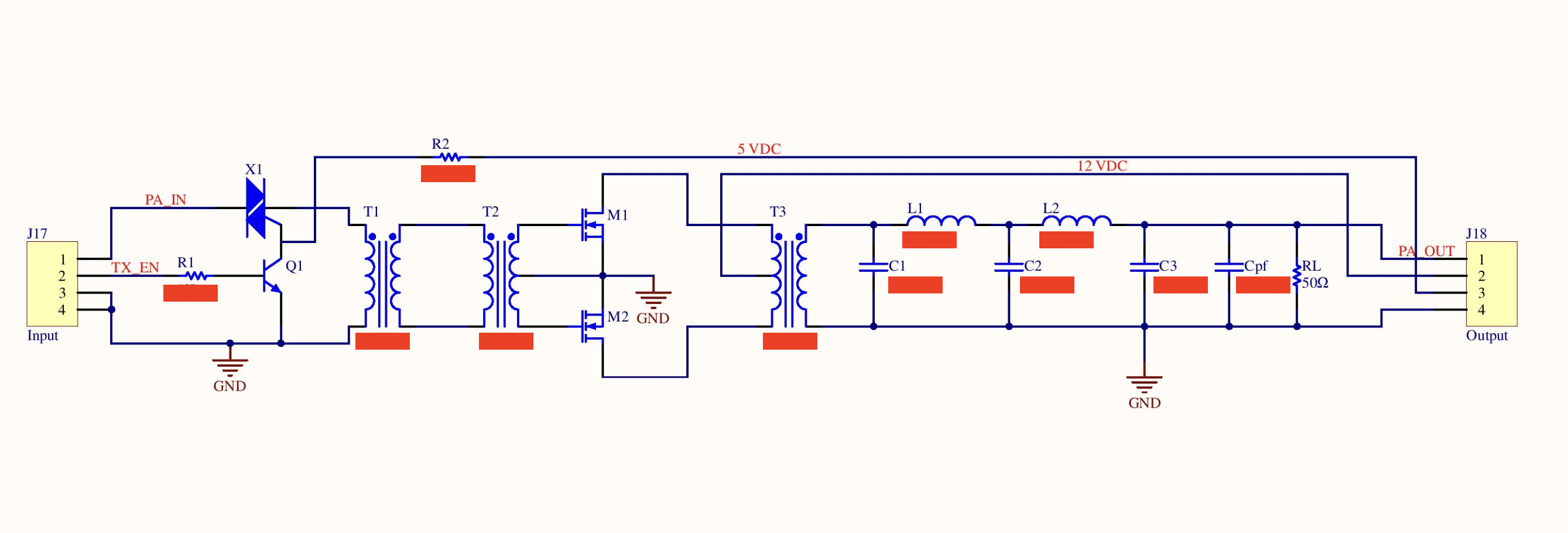

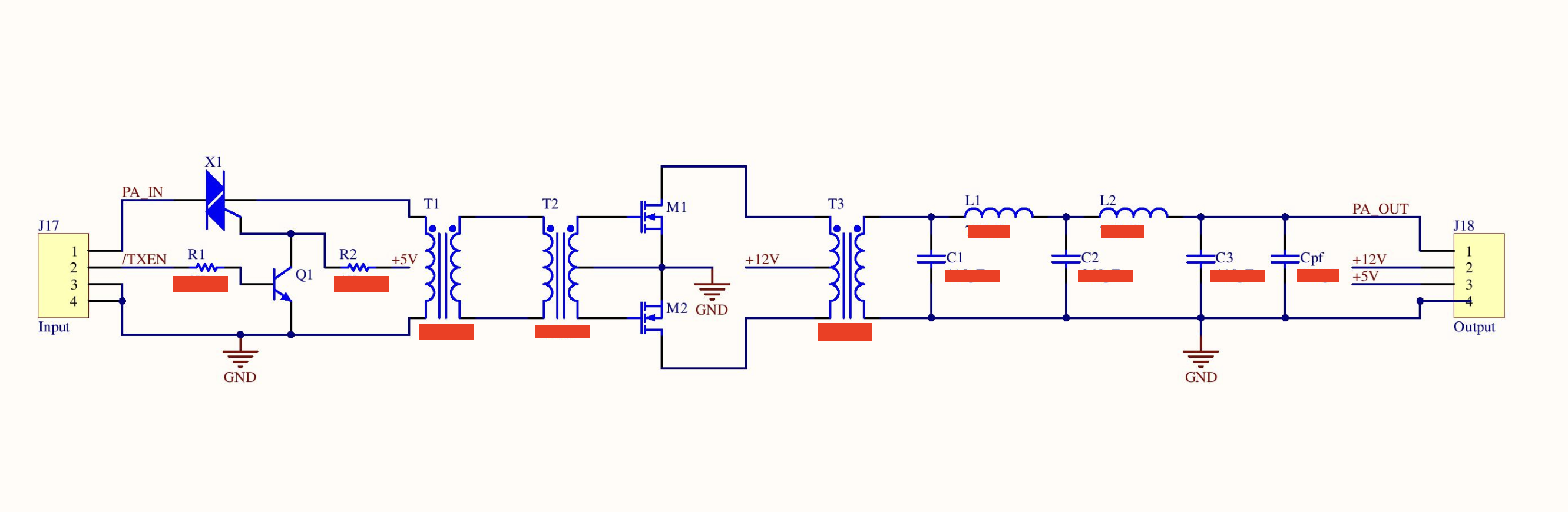

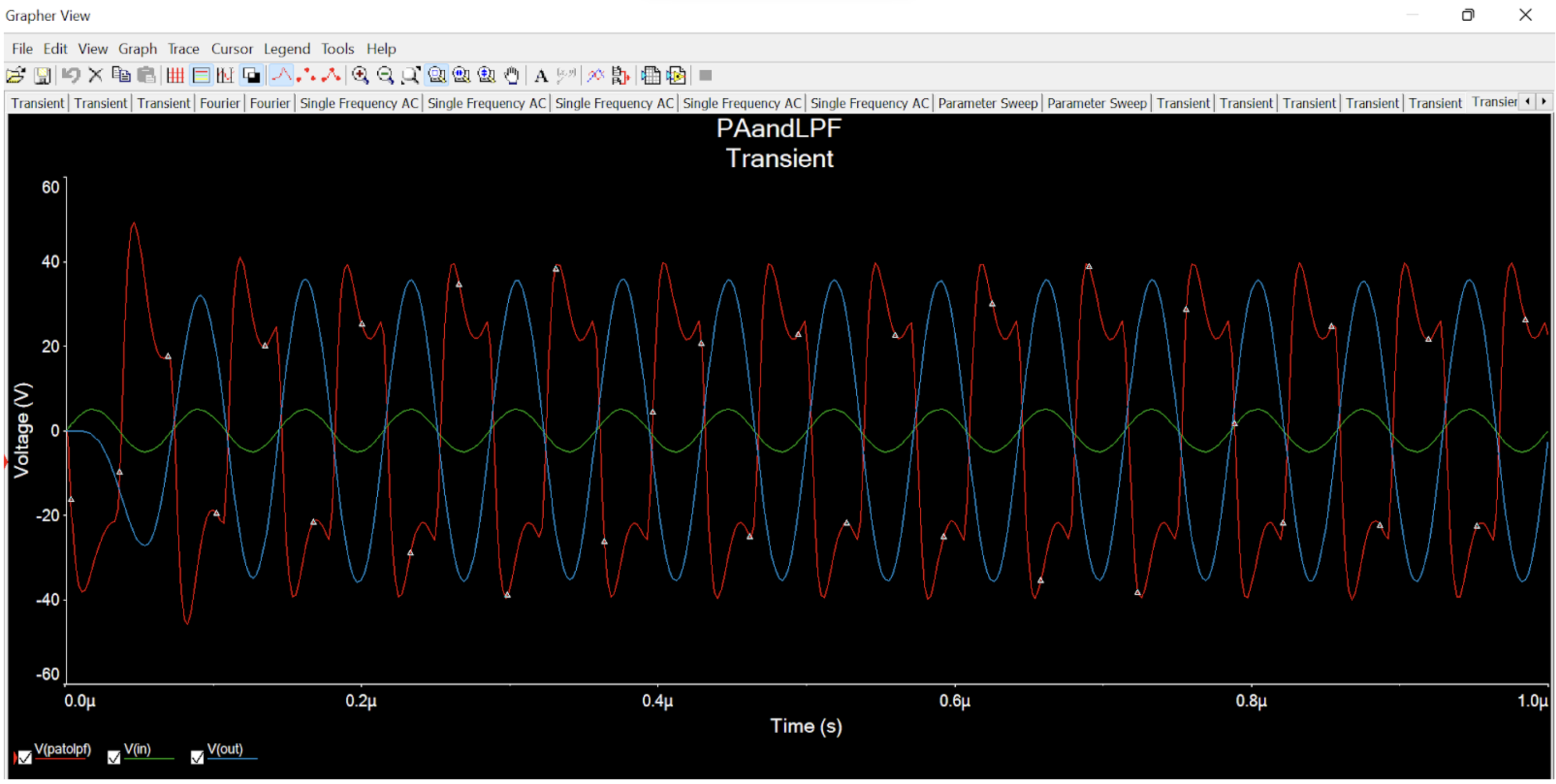

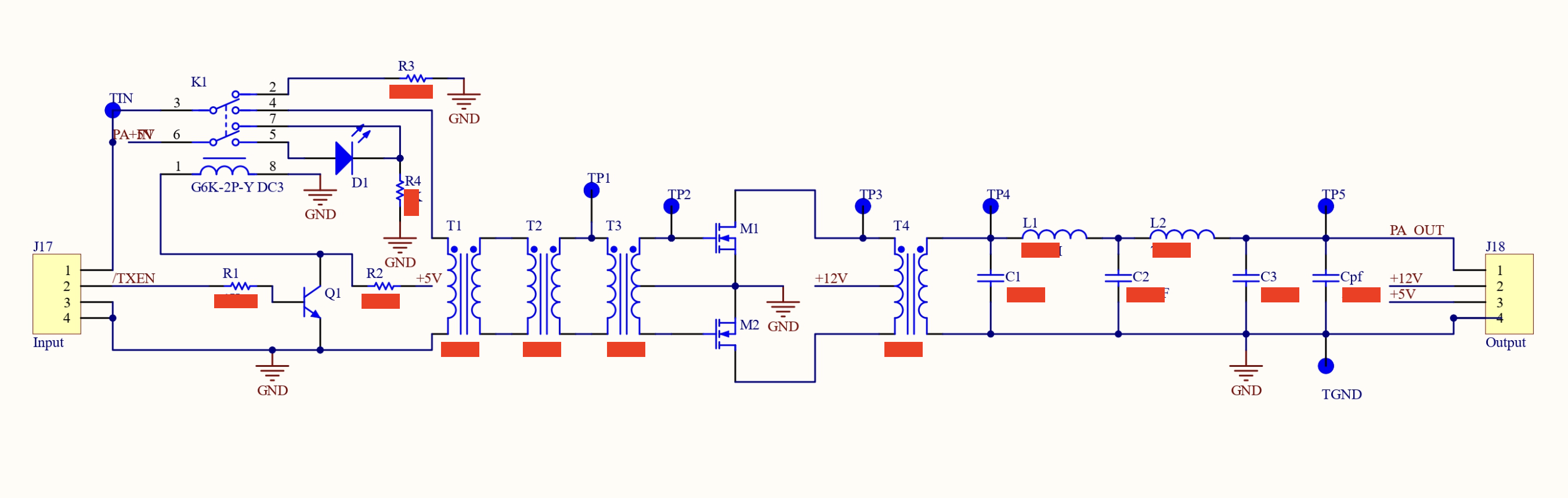

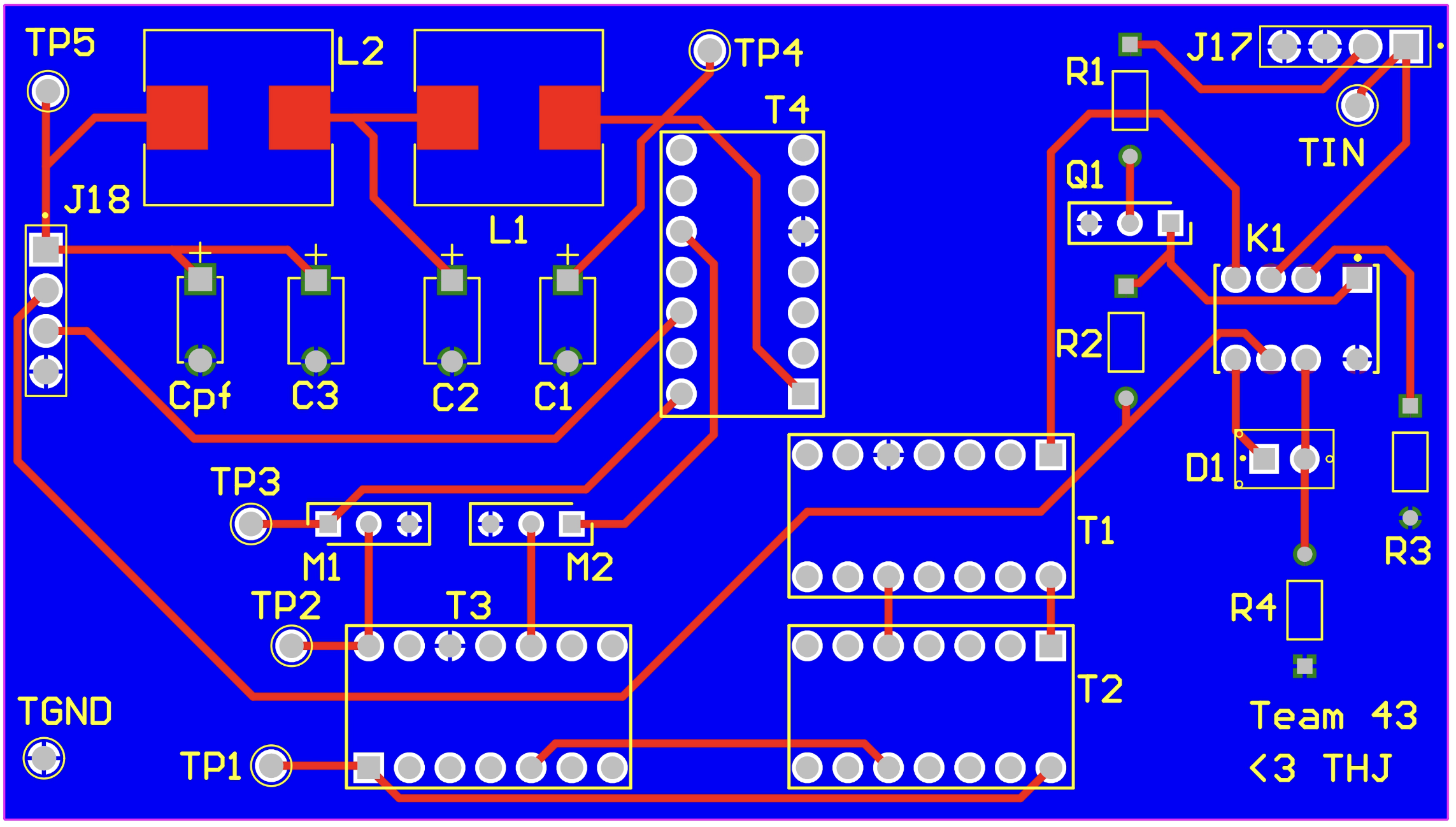

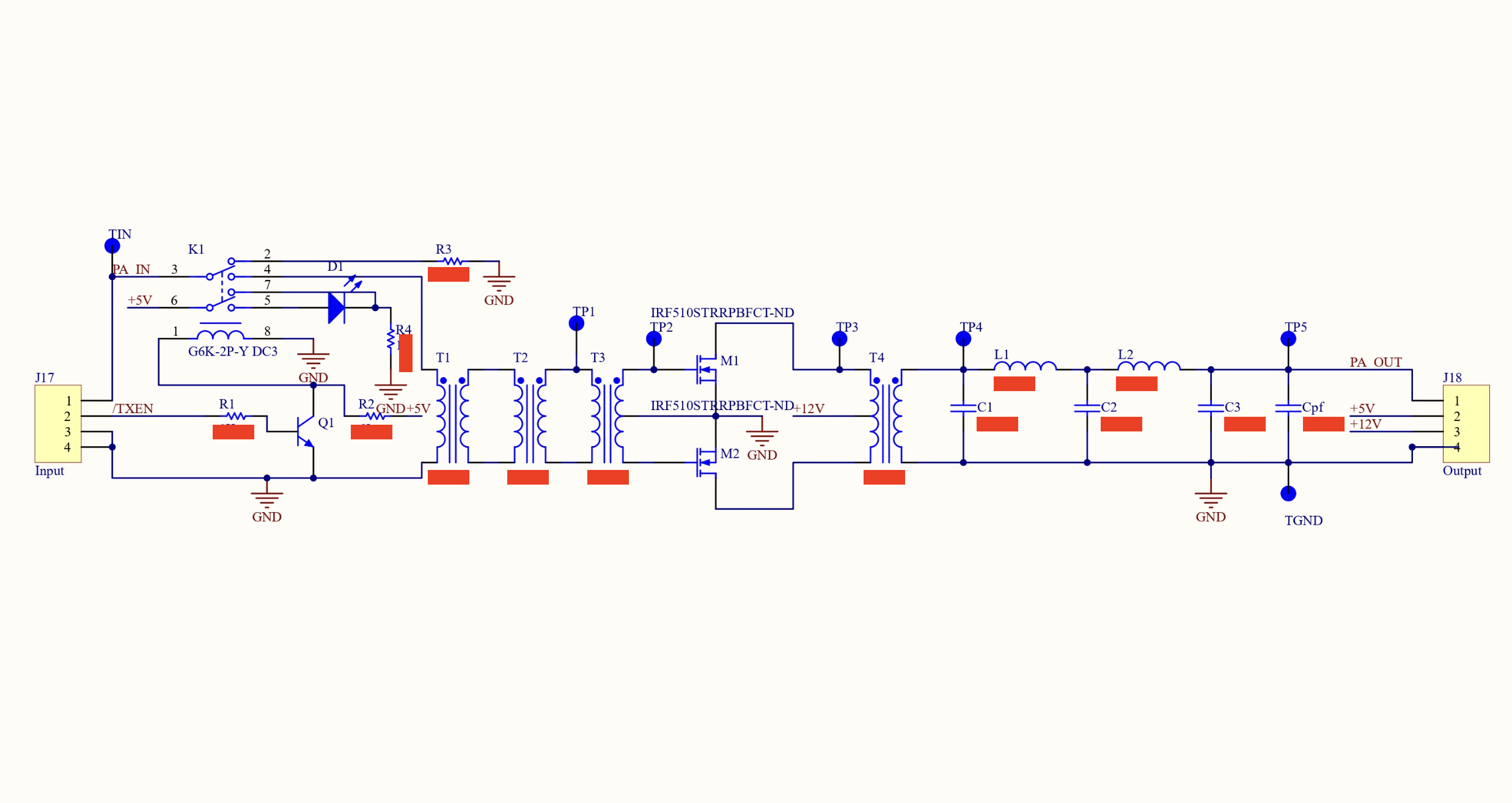

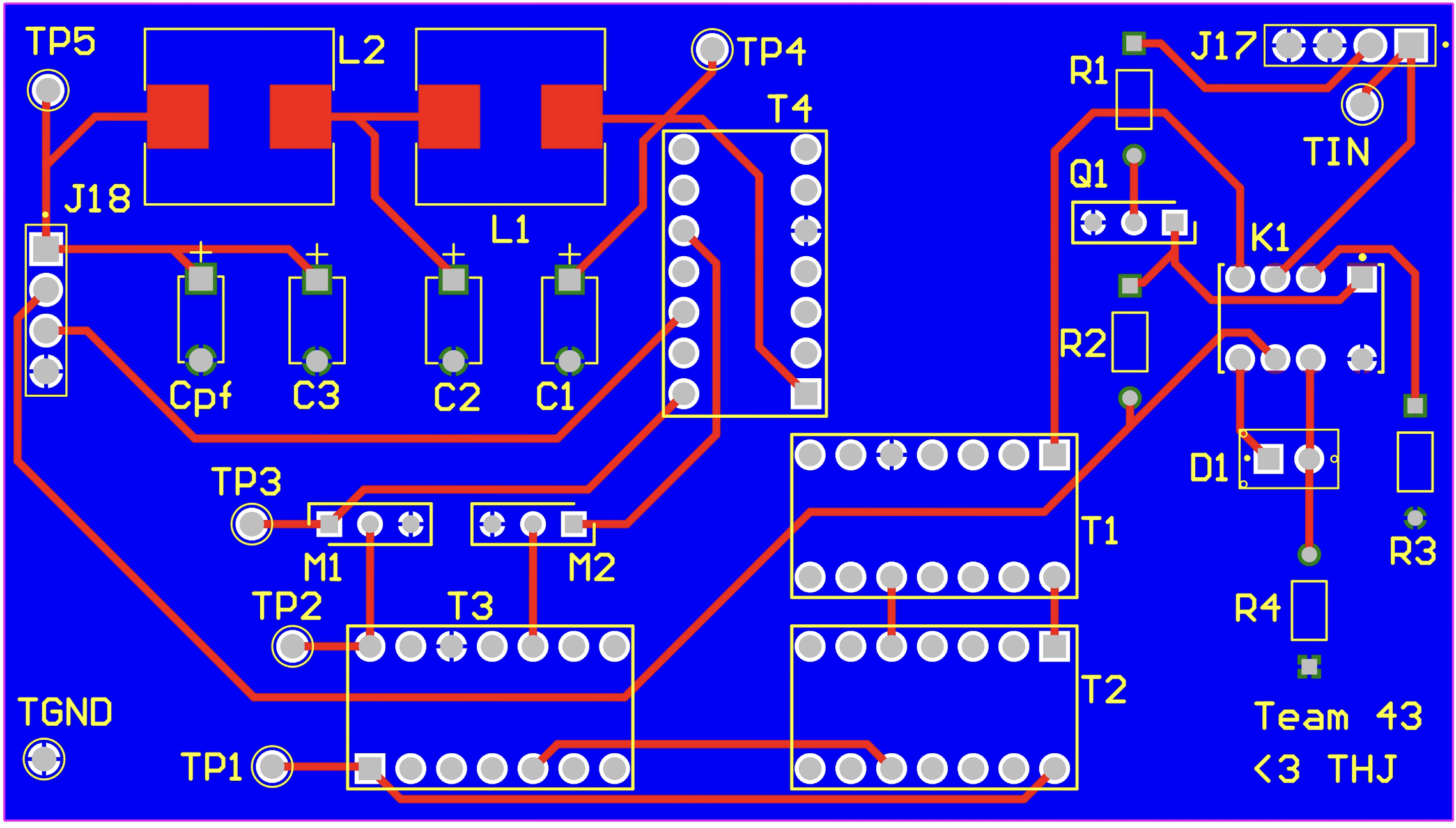

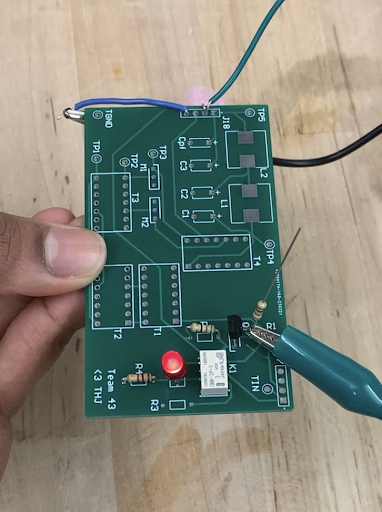

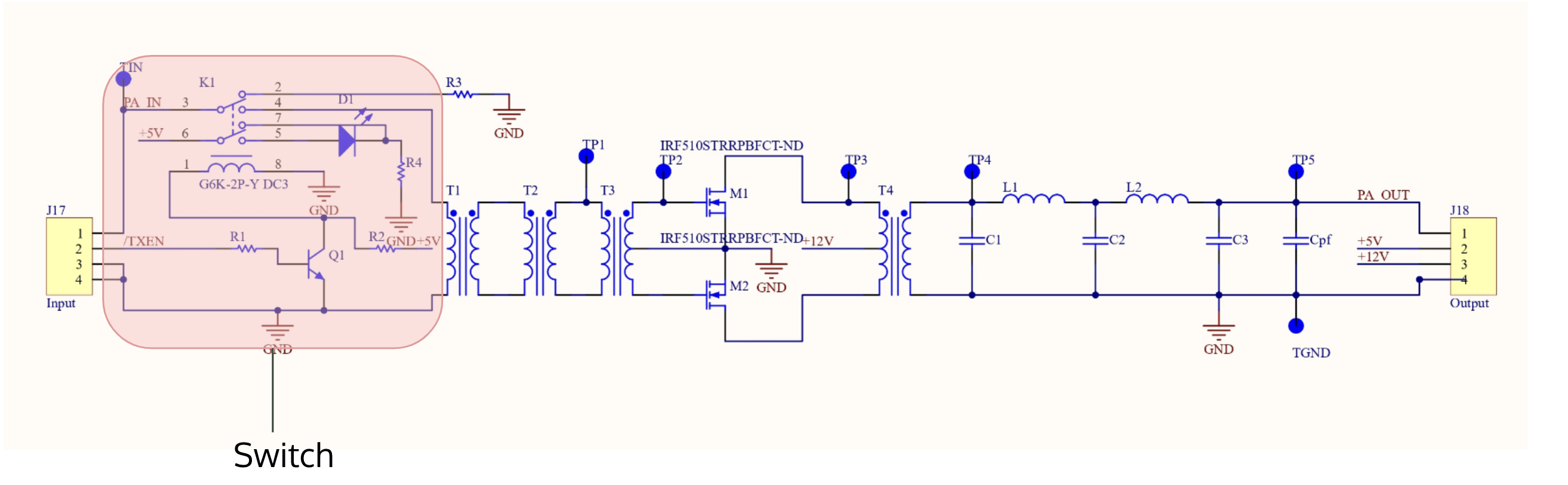

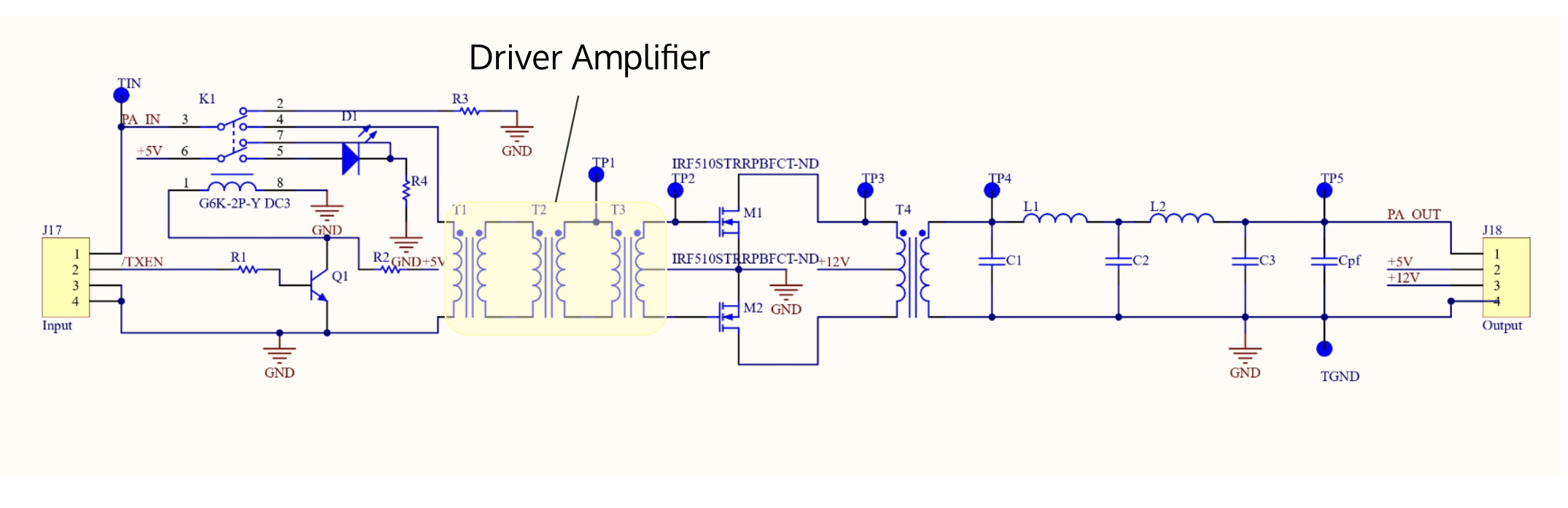

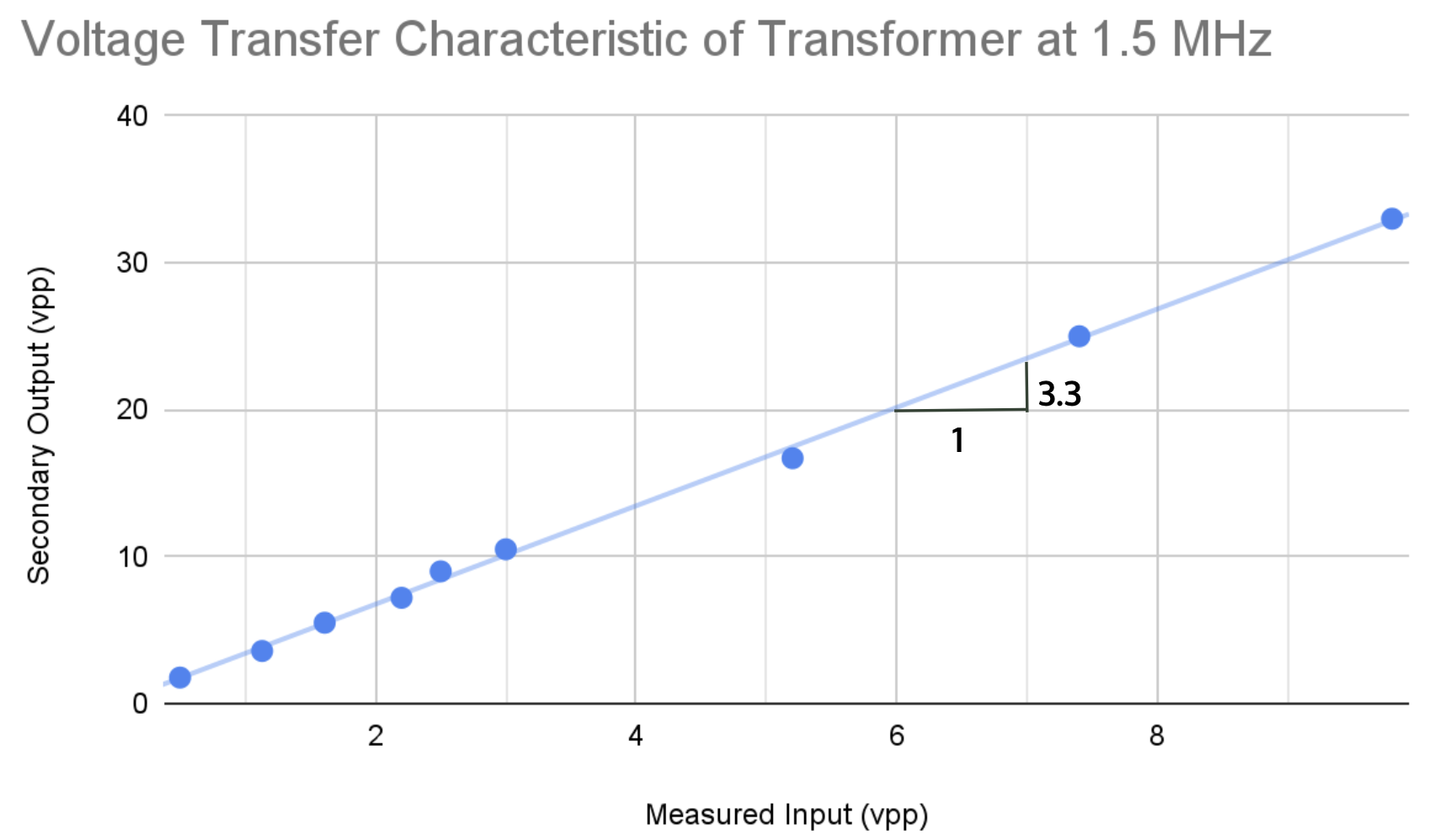

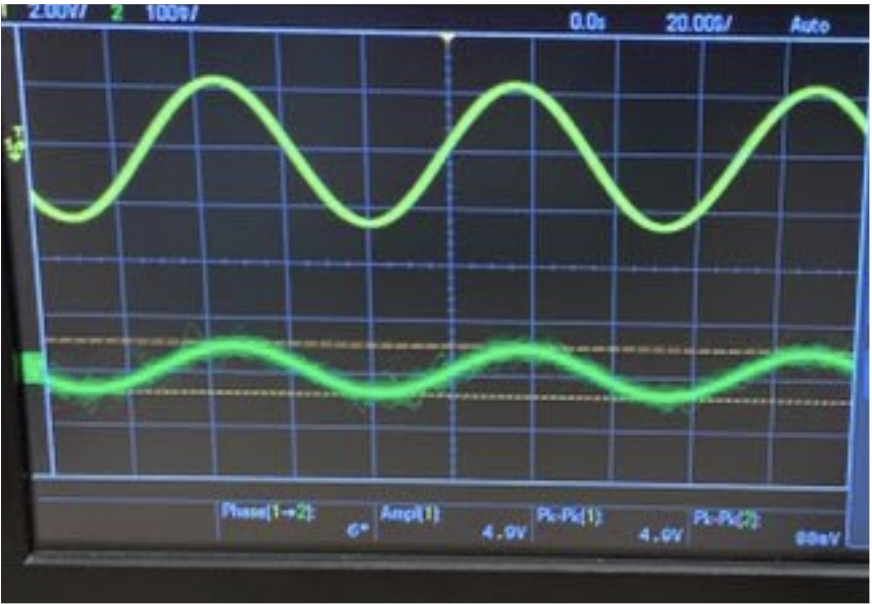

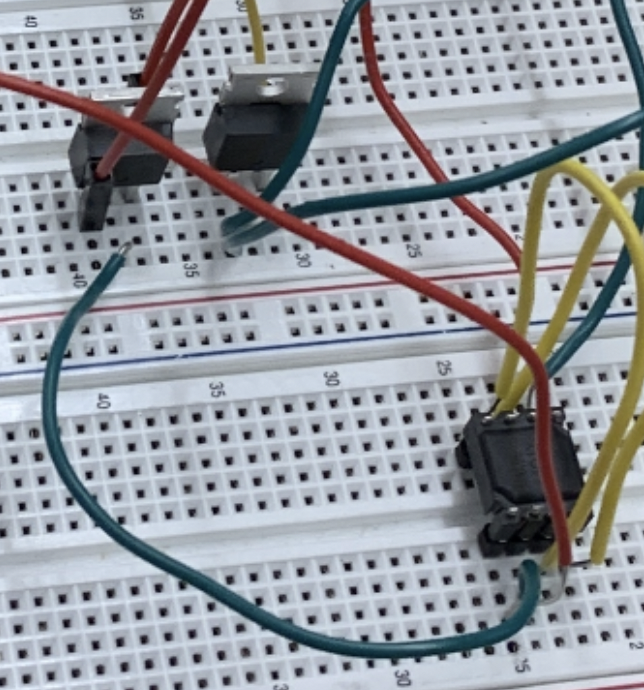

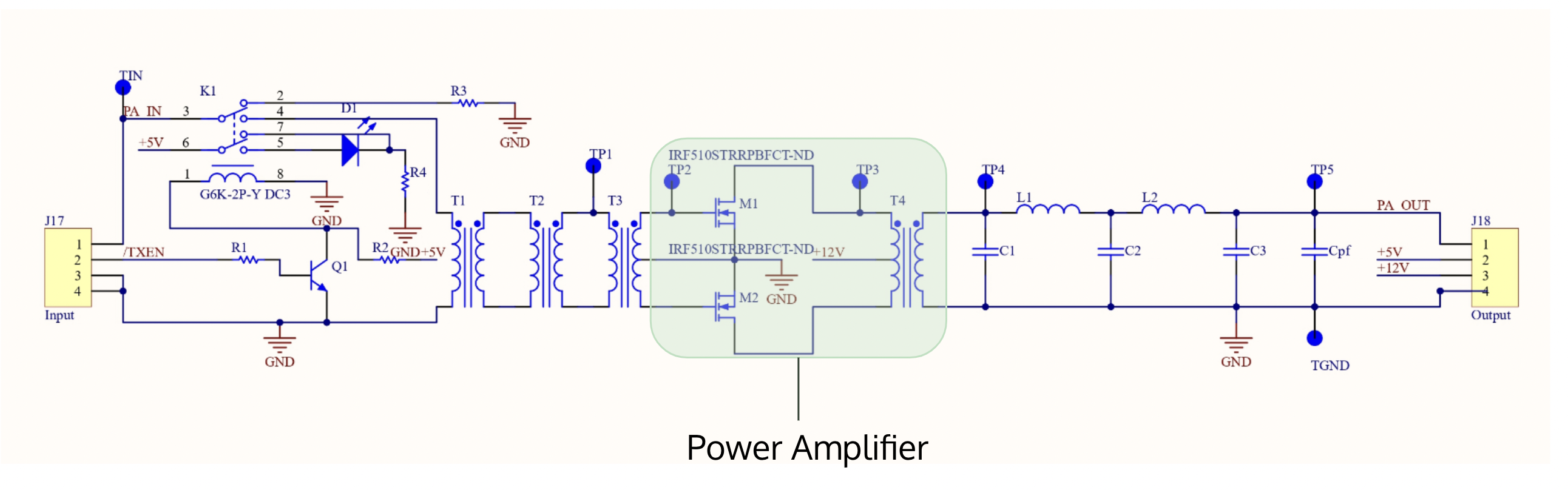

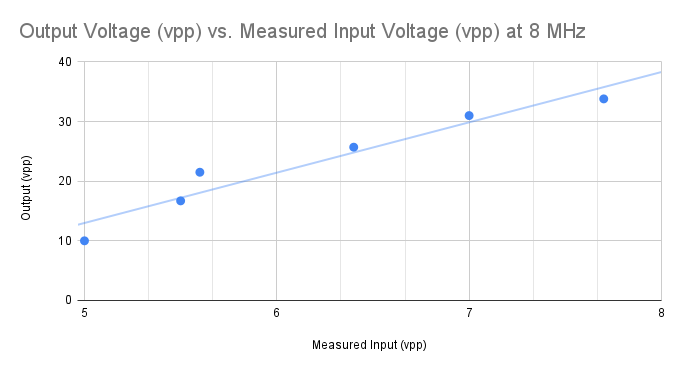

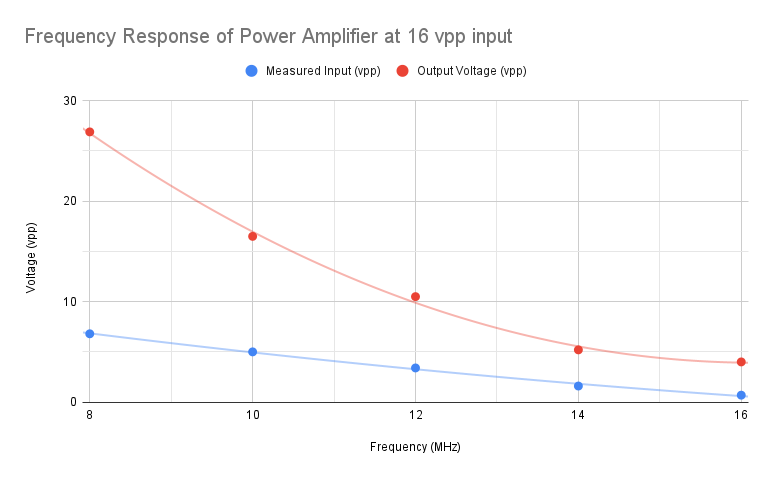

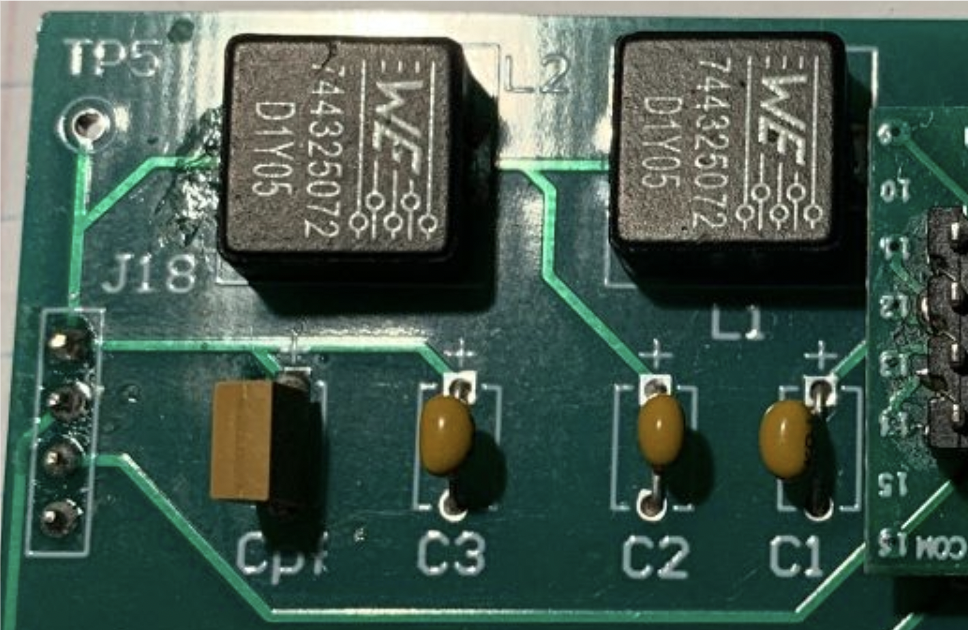

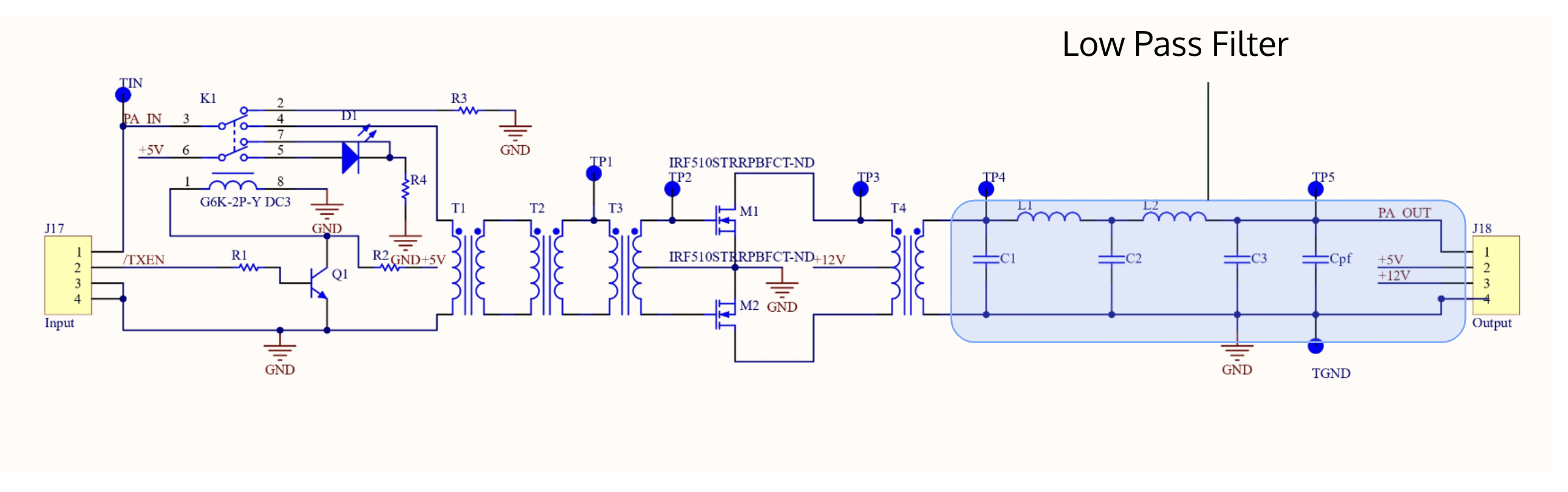

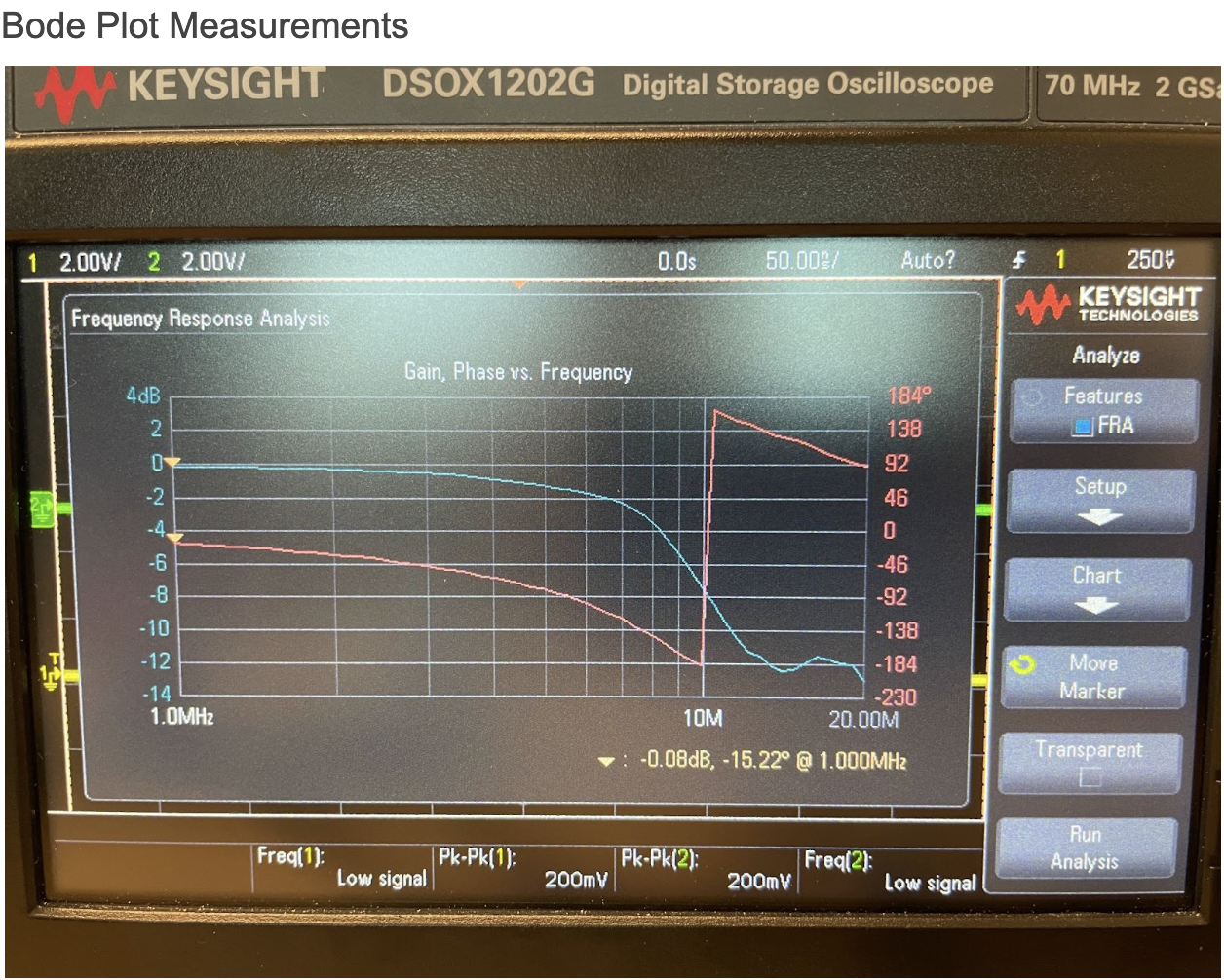

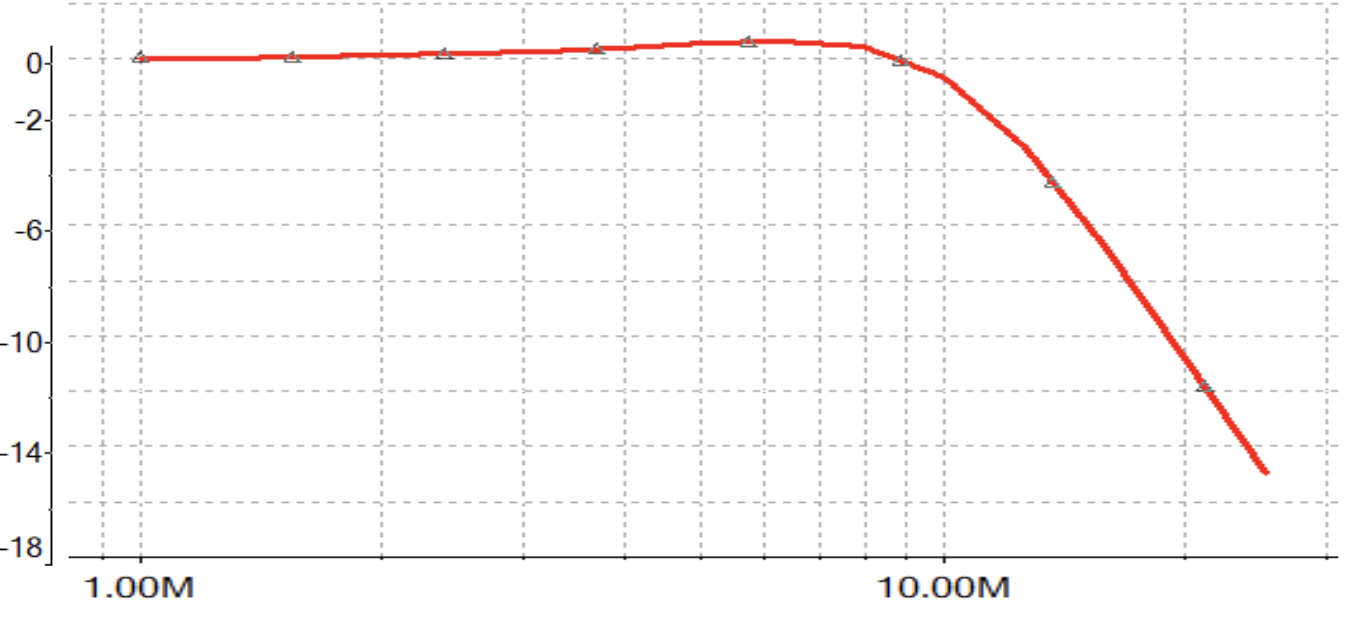

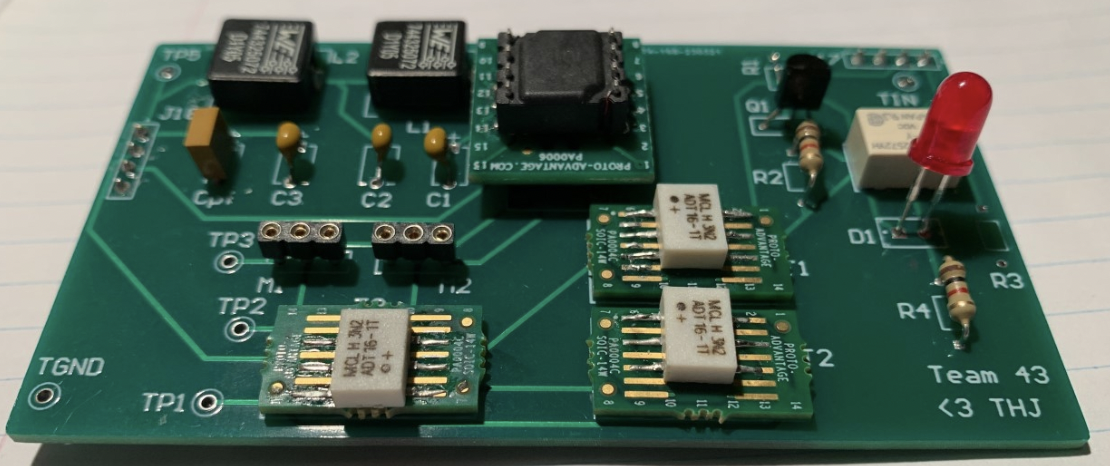

My team designed a Power Amplifier and a Low Pass filter, which is the final component in the transmitter chain. This subsystem takes the modulated signal from the mixer and amplifies it to a powerful signal that is ready to be broadcasted over long distances through the radio’s antenna. To maintain signal quality, we integrated a low pass filter to remove distortion created by the power amplifier in the process.

Our Project Management Approach:

Our team used an Agile-Waterfall hybrid approach by being flexible and iterative in the circuit design phase and more sequential in the subsequent tasks related to PCB assembly and systems integration. Over the course of the project, there were two technical design reviews, in addition to two presentations aimed at non-technical audiences. Overall, the project was structured to replicate the design cycle commonly seen in industry settings, providing students with a genuine and practical experience.

Note

To abide by the University of Toronto's Academic Integrity policies, I will not be releasing any calculations for component values.